**OPEN ACCESS**

# RESEARCH ARTICLE

# Design the High Speed Kogge-Stone Adder by Using

## MUX

Vishal Galphat, Nitin Lonbale ECE Deptt, SBITM, Betul, M.P.

#### Abstract

In this Technical era the high speed and low area of VLSI chip are very- very essential factors. Day by day number of transistors and other active and passive elements are growing on VLSI chip. In Integral part of the processor adders play an important role. In this paper we are using proposed kogge-stone adders for binary addition to reduce the size and increase the efficiency or processors speed. Proposing kogge stone adder and other adders. Here we are comparing the kogge stone adders of different-different word size from other adders. The design and experiment can be done by the aid of Xilinx 14.1i Spartan 3 device family.

**Keywords**: Kogge Stone Adder, Ripple Carry Adder, Proposed Kogge Stone Adder, 14.1i Spartan 3 Device Family.

## I. INTRODUCTION

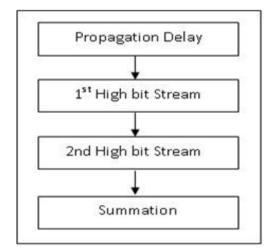

The stage of multiplication in any crucial appli-cation considered greatly influence the processor speed. The processors speed mostly depends on adder design techniques. Adder is the device by which two or more than two bit information can be added. These devices are need of hour for dig-ital signal processing and image signal processing. Vedic mathematics is the best option to calculate the fast asthmatics and logical operation in fast way. There are 16 sutras in vedic mathematics like urd-hawa triyakbhayam, Nikhilam etc. So we are kept in mind that reduce the area and logical path delay as possible as. The propagation delay is played a very important role for digital signal processing, image processing and other various suitable appli-cation..The shorter the propagation delay, the higher the speed of the circuit and vice-versa. Propagation delay should be minimizing as possible as, for high efficient addition. For better explanation we can take instance for N bit addition in which generally propagation delay is occurred highly. When we add one high bit information(A0; A1; A2; A3) to another high bit information(B0; B1; B2; B3), carry bit(C0; C1; C2; C3) is occurred due to normally binary addition operation. This carry propagates to next bit and now bit addition is performed by 3 bit adder. So carry will propagate to the next bit over and over, this cause propagation delay will be occurred. We have principal component for 2 and 3 bit addition such as half and full adder. There another serial and parallel adder to design fast processing adder like compressor, Ripple carry adder, look a head adder etc.

Fig. 1. A Propagation delay for bit binary addition

#### **II. OBJECTIVE**

The bottleneck motive the work is to design and implement a high speed adder. Which can be used in any processor based application. Here we are proposing a Kogge stone adder (KSA) by using MUX to reduce the propagation delay.

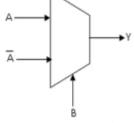

Fig. 2. A MUX blockdiagram for working as a XOR gate

#### III. MUX AS A XOR GATE

XOR gate is the special type of gate which is represented by plus sign with encirclement. The

matter of complexity can be reduced by the aid of designing of the gates. Less number of gates provides the less area for attractive designing in digital processing. Xor gate is comprised with five gates (Two AND, two NOT and one OR gate). XOR gate can also be replaced by Multiplexer (MUX). In digital electronics we are having two types of universal gates like NAND and NOR gate. By using any universal gate we can design any type of gate. Likewise MUX behaves like as universal gate that means by using mux any type of gate can be designed. To design the 2 inputs XOR gate one input of MUX must be invert to the other and both input would be connected together. Another input of XOR gate would be applied to the select line of the MUX.

So, the output of the MUX would be as same as the output of XOR Gate. The advantage of this type of designing that is Differential Cascode Voltage Switch Logic (DCVSL) as a MUX is that it produces both true and complementary outputs when provided with true and complementary inputs.

### IV. DIFFERENTIAL CASCODE VOLTAGE SWITCH LOGIC (RCA)

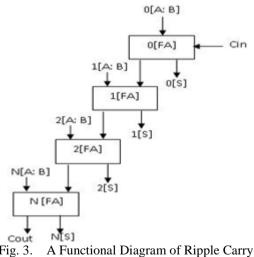

A ripple carry adder is a parallel digital adder circuit that produces the arithmetic sum of two binary numbers. It can be comprised with full adders connected in cascaded, with the carry output from each full adder connected to the carry input of the next full adder in the chain. This kind of adder is typically known as Ripple Carry Adder because carry ripples to next full adder. The layout of Ripple Carry Adder is simple, which allows fast design

Fig. 3. A Functional Diagram of Ripple Carr Adder

time. The Ripple Carry Adder is slowest among all the adders because every full adder must wait till the previous full adder generates the carry bit for its input.

$$S_0 = A_0 B_0 C_{in}$$

(1)

$$C_0 = (A_0 B_0) + (B_0 C_{in}) + (C_{in} A_0)$$

(2)

www.ijera.com

$\mathbf{S}_1 = \mathbf{A}_1 \mathbf{B}_1 \mathbf{C}_0 \tag{3}$

$$C_1 = (A_1B_1) + (B_1C_0) + (C_0A_1)$$

(4)

$$\mathbf{S}_2 = \mathbf{A}_2 \mathbf{B}_2 \mathbf{C}_1 \tag{5}$$

$$C_2 = (A_2B_2) + (B_2C_1) + (C_1A_2)$$

(6)

S = A B C (7)

$$C_{n} = (A_{n} B_{n}) + (B_{n} C_{n-1}) + (C_{n-1} A_{n})$$

(8)

The ripple carry adder has the smallest are when compare to other adder. it is limited to application where the area and propagation delay must be minimized. As we can see in diagram of ripple carry adder which has much more number of gates. Ripple carry adder does not provide efficient area and speed because of its complexity.

#### V. KOGGE-STONE ADDER

The Kogge-Stone adder concept was developed by Peter M. Kogge and Harold S. Stone, which they published in 1973 in a seminal paper titled. KS adder is the special and fast adder. Kogge stone adder is comprised with three units such as pre processing, carry generator and post processing unit.

$$\mathbf{P} = \mathbf{A}_{i}\mathbf{B}_{i} \tag{9}$$

$$\mathbf{G} = \mathbf{A}_{i}\mathbf{B}_{i} \tag{10}$$

$$\mathbf{C}_{i} = \mathbf{G}_{i} \tag{10}$$

$$\mathbf{S}_{i} = \mathbf{P}_{i} \mathbf{C}_{i-1} \tag{12}$$

**59** | P a g e

In kogge stone adder XOR can be replaced by MUX which provide different structure and gives the true and complement value at a time.

TABLE I COMPRESION OF DIFFERENT TYPES OF ADDER WITH KSA BY MUX

| ADDER WITH KSA DI MUA |                |      |             |

|-----------------------|----------------|------|-------------|

| Bit size              | Adder          | Area | Delay in ns |

| 8 bit                 | Regular(RCA)   | 144  | 11.92       |

| SQRT                  | BEC            | 132  | 13.69       |

| CSLA                  | Modified (CBL) | 111  | 11.15       |

|                       | KSA by MUX     | 83   | 5.776       |

| 16 bit                | Regular (RCA)  | 348  | 16.15       |

| SQRT                  | BEC            | 291  | 18.77       |

| CSLA                  | Modified (CBL) | 276  | 15.48       |

|                       | KSA by MUX     | 166  | 12.85       |

| 32 bit                | Regular (RCA)  | 698  | 28.97       |

| SQRT                  | BEC            | 762  | 34.44       |

| CSLA                  | Modified (CBL) | 552  | 26.23       |

|                       | KSA by MUX     | 332  | 24.56       |

| 64 bit                | Regular (RCA)  | 1592 | 52.82       |

| SQRT                  | BEC            | 1498 | 64.61       |

| CSLA                  | Modified (CBL) | 1104 | 47.74       |

|                       | KSA by MUX     | 664  | 45.25       |

|                       | I              |      |             |

## VI. CONCLUSION AND FUTURE WORK

Eventually a novel high speed adder can be implemented by different structure of kogge stone adder. Simulation result is implementing on Xilinx 14.2i Spartan 3E advanced VHDL software tool. This experiment gives better result than other adder apart from that it gives less area and low propagation delay. In future this adder can be helped to design a high speed multiplier which is essential for digital processor. Apart from that these fast adder and multiplier can be used for convolution and deconvolution.

## REFERENCES

- [1] Youngjoon Kim and Lee-Sup Kim, 2001.A low power carry select adder with reduced area,IEEE International Symposium on Circuits and Systems, vol.4, pp.218-221.

- [2] Akhilesh Tyagi,1990.A Reduced Area Scheme for Carry- Se-lect Adders,IEEE International Conference on Computer design, pp.255-258.

- [3] Belle W.Y.Wei and Clark D.Thompson,1990.Area-Time Optimal Adder Design, IEEE transactions on Computers, vol.39, pp. 666-675.

- [4] Kogge P and Stone H, 1973.A Parallel Algorithm for the Efficient Solution of a General Class of Recurrence Relations, IEEE Transactions on Computers, Vol. C-22, No. 8, pp. 786-793.

- [5] Madhu Thakur and Javed Ashraf, 2012.Design of Braun Mul-tiplier with Kogge-Stone Adder and Its Implementation on FPGAInternational Journal of Scientific and Engineering Re-search, Vol. 3, No. 10, pp. 03-06, ISSN 2229-5518.

- [6] Somayeh Babazadeh and Majid Haghparast, 2012.Design of a Nanometric Fault Tolerant Reversible Multiplier Circuit, Journal of Basic and Applied Scientific Research.

- [7] Sumeer Goel, Mohammed A. Elgamel, Magdy A. Bay-oumi, Yasser Hanafy, 2006.Design Methodologies for High-Performance Noise-Tolerant XOR-XNOR Circuits,IEEE Transac-tions on Circuits and Systems- I, Vol. 53, No. 4, pp. 867-878.

- [8] Mohammad Shamim Imtiaz, Md Abdul Aziz Suzon, Mahmudur Rahman,2012.Design of Energy efficient Full adder using hybrid CMOS logic styleInternational Journal of Advances in Engineer-ing and Technology, Jan 2012.

- [9] Ila Gupta, Neha Arora, Prof. B.P. Singh, 2012.Analysis of Several 2:1 Multiplexer Circuits at 90nm and 45nm Technologies,International Journal of Scientific and Research Publica-tions, Volume 2, Issue 2, February 2012.